MBaRZG2x DIP switch settings

Boot Mode DIP Switch Settings

Default positions of DIP switches S2, S3, S4 and S5 when using a TQMaRZG2x:

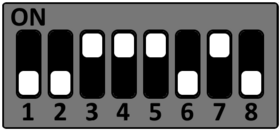

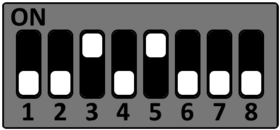

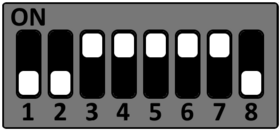

eMMC Boot

S2

S3

S4

S5

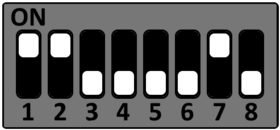

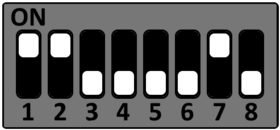

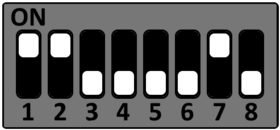

QSPI Boot

S2

S3

S4

S5

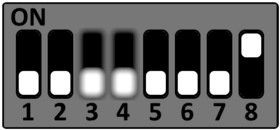

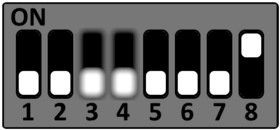

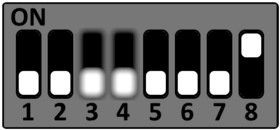

Serial Downloader

S2

S3

S4

S5

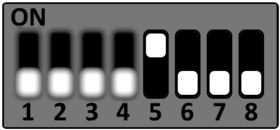

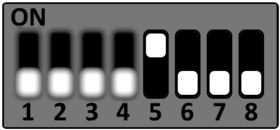

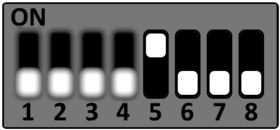

Functional DIP Switches

Detailed DIP Switch Settings

S2

| DIP | Function | default position |

|---|---|---|

| 1 | Cortex Type selection | OFF |

| 2 | OFF | |

| 3 | Normal Boot Mode | ON |

| 4 | Boot Device Config | |

| 5 | ||

| 6 | ||

| 7 | ||

| 8 | Reserved | OFF |

S3

| DIP | Function | default position |

|---|---|---|

| 1 | AArch selection: OFF: AArch32 ON: AArch64 | ON |

| 2 | EXTAL Frequency | ON |

| 3 | OFF | |

| 4 | Function select: OFF: PCIe ON: SATA | RZ/G2M = OFF RZ/G2H or N = not used |

| 5 | JTAG (see Reference Manual) | not used |

| 6 | ||

| 7 | Clock Source: OFF: External Clock input ON: use Crystal resonator | ON |

| 8 | EXBUS Data Bus Width | not used |

S4

| DIP | Function | default position |

|---|---|---|

| 1 | Reserved | OFF |

| 2 | LPDDR4 Dip 2 | OFF |

| 3 | JTAG (see Reference Manual) | not used |

| 4 | JTAG (see Reference Manual) | not used |

| 5 | DDR Frequency DIP 1 | OFF |

| 6 | Division Ratio of PLL1 | OFF |

| 7 | DDR Frequency DIP 2 | OFF |

| 8 | Reserved | ON |

S5

| DIP | Function | default position |

|---|---|---|

| 1 | Not Connected | not used |

| 2 | ||

| 3 | JTAG (see Reference Manual) | not used |

| 4 | JTAG (see Reference Manual) | not used |

| 5 | RCLK Source | ON |

| 6 | LPDDR4 Dip 1 | OFF |

| 7 | Reserved | OFF |

| 8 |

S10

| DIP | OFF | ON |

|---|---|---|

| S10-1 | PCIe | SATA |

| S10-2 | MSIOF2 on MicroBus (D12) | MSIOF2 on RGB Display (X12) |

| S10-3 | 5V Fan (x30) | 12V Fan (x30) |

| S10-4 | UART0: Pin Header (x33) UART2: Not Connected | UART0: microUSB (x9) UART2: microUSB (x9) |

CAN configuration (S1)

DIP switch S1 is used to configure the CAN interfaces CAN1 and CAN2.

| DIP | OFF (default) | ON |

|---|---|---|

| S1-1 | CAN1 not terminated | CAN1 interface terminated (120Ω) |

| S1-2 | CAN2 not terminated | CAN2 interface terminated (120Ω) |