Configuring the GPIOs

If you want to use certain pins of the TQMa35 as GPIO and configure their characteristics, you must turn on both the GPIO's support for the Linux kernel, as well as explicitly request the pin as GPIO in the kernel driver for the board. The pin configuration can also be set in the driver.

Linux kernel

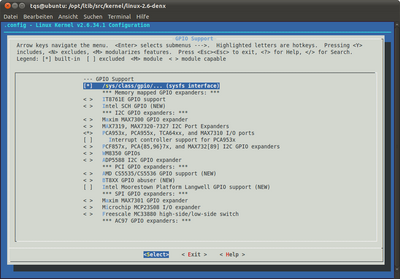

Activate under Device Drivers —> GPIO Support —> /sys/class/gpio/… (sysfs interface) in the kernel configuration.

Then recompile and install the kernel.

By this the kernel supports the integration of GPIOs and access to those in sysfs. For support in the driver the appropriate board support file must be opened in the Linux source (in case of the TQMa35 arch/arm/mach-mx3/mach-tqma35.c). Each pin has a primary and several alternate functions. To use the alternate function GPIO pin, you create a macro with the primary name and the desired function of the pin, which resolves to a further macro “IOMUX_PAD”. This contains the pin configuration.

If you want to use for example pin TX2_RX3 as GPIO, you create the macro MX35_PAD_TX2_RX3__GPIO1_13. GPIO1, because TX2_RX3 is located at GPIO port 1 and is the 13th pin there.

#define MX35_PAD_TX2_RX3__GPIO1_13

To configure the pin correctly a definition has to be added to this macro. This is done by the macro IOMUX_PAD:

#define IOMUX_PAD(_pad_ctrl_ofs, _mux_ctrl_ofs, _mux_mode, _select_input_ofs, _select_input, _pad_ctrl)

The parameters for this macro describe the properties of the pin. This data is to be taken from the data sheet of the i.MX35, appendix A, “IOMUX registers”.

_pad_ctrl_ofs - hexadecimal offset of the control register, which selects the electrical circuitry (from page 2336 in IMX35RM.pdf) _mux_ctrl_ofs - hexadecimal offset of the MUX control register, which selects the function of the pin _mux_mode - bits 2..0 in MUX control register _select_input_ofs - SELECT_INPUT register offset (see table 4-11 IOMUX_CTL Register Addresses from 0x07A8, IMX35RM.pdf) _select_input - see table 4-12 Daisy Chain List, IMX35RM.pdf _pad_ctrl - bits to be set in register _pad_ctrl_ofs for configuration selection

In the example of pin TX2_RX3 the macro must be defined as follows:

#define MX35_PAD_TX2_RX3__GPIO1_13 IOMUX_PAD(0x5a8, 0x164, 5, 0x0, 0, PAD_CTL_PKE | PAD_CTL_PUE | (0 << 5) | PAD_CTL_PUS_100K_DOWN)

This registers the GPIO pin as with a 100k pull-down resistor.

Then the macro MX35_PAD_TX2_RX3__GPIO1_13 must be added to the list of pins to be registered (static struct pad_desc tqma35_pads[]).

After compiling the kernel and uploading the image the GPIO pin should be available under /sys/class/gpio/ when it was exported with the following command.

$ echo <pin number = (port number-1)*32 + pin number> > /sys/class/gpio/export Example: $ echo 13 > /sys/class/gpio/export

A variety of functions for GPIO are available in /sys/class/gpio/gpio13:

- the direction is set with

inoroutin the file direction

- the level of the pin can be read/set in the file value

- etc.

Literature

- Section 4.2 Pin-Muxing Control in the i.MX35 Reference Manual